|

|

| (53 intermediate revisions by the same user not shown) |

| Line 7: |

Line 7: |

| | 2 RAMs are connected to CycloneV's [[APF6_SP]]. | | 2 RAMs are connected to CycloneV's [[APF6_SP]]. |

| | | | |

| − | == Simplified view == | + | == Parameters == |

| − | {{Under_Construction}}

| + | * DDR3: |

| − | == Pinout placement== | + | {| border="1" cellpadding="5" cellspacing="0" |

| | + | |+[http://www.micron.com/parts/dram/ddr3-sdram/mt41k128m16jt-125 MT41K128M16JT-125] |

| | + | |- |

| | + | |part |

| | + | |MT41K128M16JT-125 |

| | + | |- |

| | + | |type |

| | + | |DDR3L |

| | + | |- |

| | + | |Speed (DDR) |

| | + | |750Mhz |

| | + | |- |

| | + | |timings |

| | + | |See verilog model [http://www.micron.com/~/media/documents/products/sim-model/dram/ddr3/ddr3-sdram-verilog-model.zip provided by micron] |

| | + | |- |

| | + | |JEDEC |

| | + | | JEDEC DDR3-1600 -> JEDEC DDR3-1G6 2GB x8 |

| | + | |- |

| | + | |Chip size |

| | + | |2048Mbits -> 128M x 16bits |

| | + | |} |

| | | | |

| − | <pre>

| + | == General description == |

| − | set_location_assignment PIN_C11 -to mem_a[0]

| + | |

| − | set_location_assignment PIN_B11 -to mem_a[1]

| + | |

| − | set_location_assignment PIN_A8 -to mem_a[2]

| + | |

| − | set_location_assignment PIN_A7 -to mem_a[3]

| + | |

| − | set_location_assignment PIN_D11 -to mem_a[4]

| + | |

| − | set_location_assignment PIN_E11 -to mem_a[5]

| + | |

| − | set_location_assignment PIN_F8 -to mem_a[6]

| + | |

| − | set_location_assignment PIN_E7 -to mem_a[7]

| + | |

| − | set_location_assignment PIN_D9 -to mem_a[8]

| + | |

| − | set_location_assignment PIN_D8 -to mem_a[9]

| + | |

| − | set_location_assignment PIN_B6 -to mem_a[10]

| + | |

| − | set_location_assignment PIN_B5 -to mem_a[11]

| + | |

| − | set_location_assignment PIN_C8 -to mem_a[12]

| + | |

| − | set_location_assignment PIN_B8 -to mem_a[13]

| + | |

| − | set_location_assignment PIN_H6 -to mem_a[14]

| + | |

| | | | |

| − | set_location_assignment PIN_C9 -to mem_ba[2]

| |

| − | set_location_assignment PIN_C10 -to mem_ba[1]

| |

| − | set_location_assignment PIN_C6 -to mem_ba[0]

| |

| | | | |

| − | set_location_assignment PIN_A10 -to mem_cas_n[0]

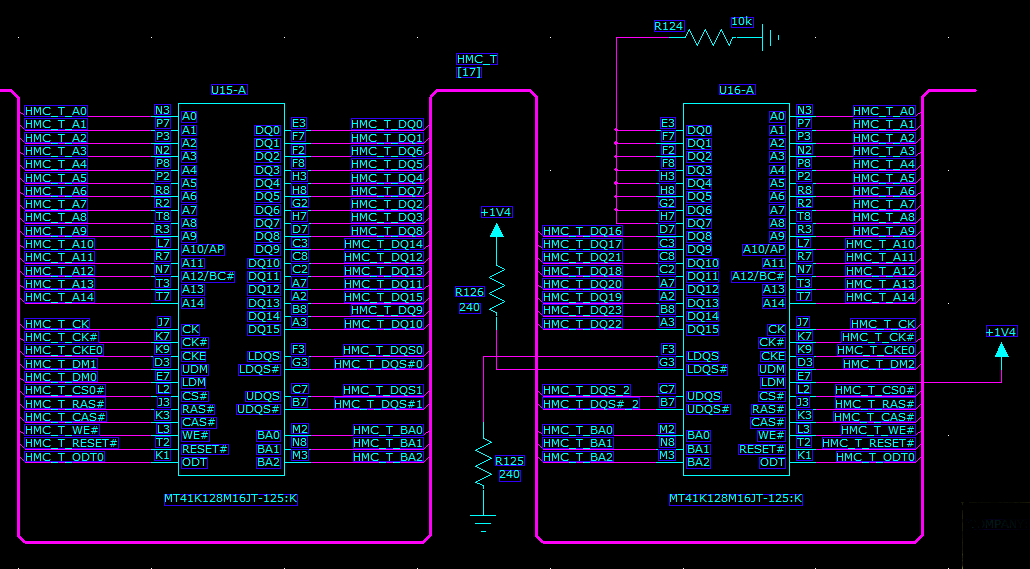

| + | Diagram below describe the connections between the CycloneV and the two DDR3 blocks. Each DDR3 blocks has two banks of 128MB, on one chip (U15) all data are used, and on the other chip, only 128MB are used, the second bank is not plugged. Thus, the amount of ram accessible via the fpga is 384MB, with a data bus of 24bits. |

| − | set_location_assignment PIN_J9 -to mem_ck[0]

| + | |

| − | set_location_assignment PIN_J8 -to mem_ck_n[0]

| + | |

| − | set_location_assignment PIN_H8 -to mem_cs_n[0]

| + | |

| | | | |

| − | set_location_assignment PIN_C21 -to mem_dm[2]

| + | [[File:imx6-cycloneV-ddr3.png|frame|center| DDR wiring diagram. Each green arrow is a 8 bits part of the data bus]] |

| − | set_location_assignment PIN_C19 -to mem_dm[1]

| + | |

| − | set_location_assignment PIN_A15 -to mem_dm[0]

| + | |

| | | | |

| − | set_location_assignment PIN_C20 -to mem_dq[23]

| + | To use the DDR3 SDRAM Controller with UniPhy provided by Quartus to instanciate the DDR3. See above how to do with Qsys. |

| − | set_location_assignment PIN_B20 -to mem_dq[22]

| + | |

| − | set_location_assignment PIN_D18 -to mem_dq[21]

| + | |

| − | set_location_assignment PIN_E17 -to mem_dq[20]

| + | |

| − | set_location_assignment PIN_A22 -to mem_dq[19]

| + | |

| − | set_location_assignment PIN_A20 -to mem_dq[18]

| + | |

| − | set_location_assignment PIN_E16 -to mem_dq[17]

| + | |

| − | set_location_assignment PIN_D17 -to mem_dq[16]

| + | |

| | | | |

| − | set_location_assignment PIN_C18 -to mem_dq[15]

| + | [[File:apf6_sp_ddr_sch.png|frame|center|DDR3 wiring for FPGA on apf6_sp]] |

| − | set_location_assignment PIN_B16 -to mem_dq[14]

| + | |

| − | set_location_assignment PIN_C16 -to mem_dq[13]

| + | |

| − | set_location_assignment PIN_C15 -to mem_dq[12]

| + | |

| − | set_location_assignment PIN_A17 -to mem_dq[11]

| + | |

| − | set_location_assignment PIN_B18 -to mem_dq[10]

| + | |

| − | set_location_assignment PIN_F15 -to mem_dq[9]

| + | |

| − | set_location_assignment PIN_E14 -to mem_dq[8]

| + | |

| − | set_location_assignment PIN_A14 -to mem_dq[7]

| + | |

| − | set_location_assignment PIN_C14 -to mem_dq[6]

| + | |

| − | set_location_assignment PIN_D13 -to mem_dq[5]

| + | |

| − | set_location_assignment PIN_C13 -to mem_dq[4]

| + | |

| − | set_location_assignment PIN_B13 -to mem_dq[3]

| + | |

| − | set_location_assignment PIN_B12 -to mem_dq[2]

| + | |

| − | set_location_assignment PIN_E12 -to mem_dq[1]

| + | |

| − | set_location_assignment PIN_F12 -to mem_dq[0]

| + | |

| | | | |

| − | set_location_assignment PIN_G15 -to mem_dqs[2]

| + | == How to integrate DDR3 chips in Qsys == |

| − | set_location_assignment PIN_G14 -to mem_dqs_n[2]

| + | |

| | | | |

| − | set_location_assignment PIN_G12 -to mem_dqs[1]

| + | === UniPhy Howto === |

| − | set_location_assignment PIN_H12 -to mem_dqs_n[1]

| + | |

| | | | |

| − | set_location_assignment PIN_H9 -to mem_dqs[0]

| + | This is a click howto configure the DDR3 controller in the [[APF6_SP]]. |

| − | set_location_assignment PIN_G8 -to mem_dqs_n[0]

| + | |

| | | | |

| − | set_location_assignment PIN_A13 -to mem_odt[0]

| + | * Once the quartus project open, select your device correctly (see the [[APF6_SP#Resources | product page]] to now the exact part name). |

| − | set_location_assignment PIN_B15 -to mem_cke[0]

| + | * In the IP Catalog, select :<pre class="config">installed IP->Library->Memory interfaces and Controllers->Memory Interfaces with UniPHY->DDR3 SDRAM Controller with UniPhy</pre> |

| − | set_location_assignment PIN_A9 -to mem_ras_n[0]

| + | * In the right frame select :<pre class="config">JEDEC DDR3-1G6 2GB x8</pre> |

| − | set_location_assignment PIN_E6 -to mem_we_n[0]

| + | * Then click on '''Apply''' |

| − | set_location_assignment PIN_B22 -to mem_reset_n

| + | * Select checkbox '''Enable Hard External Memory Interface''' (above the 6 configs tab). |

| − | set_location_assignment PIN_A12 -to oct_rzqin

| + | * Tab '''PHY Settings''': |

| | + | ** Speed grade : '''8''' |

| | + | ** Memory clock frequency : '''375Mhz''' |

| | + | ** PLL reference clock frequency : '''62.5 Mhz''' |

| | + | ** Rate on Avalon-MM Interface : '''Full''' |

| | + | ** Supply voltage : '''1.35V DDR3L''' |

| | + | * Tab '''Memory parameters''' |

| | + | ** Memory device speed grade : 400Mhz |

| | + | ** Total interface width : 24 |

| | + | ** Row address width : 14 |

| | + | * Tab '''Controller Settings''' (Optionnal if you wan't to use the two DDR3 chip) |

| | + | ** Select checkbox '''Expand Avalon-MM data for ECC''' |

| | + | ** Select 48bits instead of 32 |

| | + | * '''Finish''' |

| | + | {{Note| Using 48bits instead 32 is not standard for avalon it can be harder to connect inside your design}} |

| | | | |

| − | set_location_assignment PIN_T20 -to global_reset_n # Pulled-up on apf6sp

| + | == Clock == |

| − | set_location_assignment PIN_H10 -to pll_ref_clk # Not Connected on apf6sp

| + | |

| − | set_location_assignment PIN_R16 -to soft_reset_n # Pulled-up on apf6sp

| + | |

| | | | |

| − | # Random pinout (not used)

| + | The hard controller IP «DDR3 SDRAM Controller with UniPHY» require using and external oscillator to clock it. On APF6_SP, the all CycloneV fpga is clocked with the PCIe clock at 62.5Mhz by default. |

| − | set_location_assignment PIN_Y16 -to drv_status_fail

| + | |

| − | set_location_assignment PIN_H18 -to drv_status_pass

| + | |

| − | set_location_assignment PIN_V18 -to drv_status_test_complete

| + | |

| − | set_location_assignment PIN_J17 -to local_cal_fail

| + | |

| − | set_location_assignment PIN_J19 -to local_cal_success

| + | |

| − | set_location_assignment PIN_AA7 -to local_init_done

| + | |

| − | </pre>

| + | |

| | | | |

| − | == Technology pinout ==

| + | To force Quartus to use the coreclkout as input clock for DDR3 controller a little hack must be done after HDL code is generated. |

| | | | |

| − | <pre>

| + | === The DDR3 clock hack === |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to oct_rzqin -tag __ddr3_contr_example_if0_p0

| + | {{Note| If you include the '''.qsys''' under your Quartus project, Quartus will regenerate all the Qsys HDL/TCL code each times you synthesize your design, and will erase the modification.}} |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[0] -tag __ddr3_contr_example_if0_p0

| + | # Generate the design with Qsys |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[0] -tag __ddr3_contr_example_if0_p0

| + | ## Connect the '''pll_ref_clk''' of IP '''DDR3 SDRAM Controller with UniPHY''' on '''coreclkout''' of '''Avalon-MM Cyclone V Hard IP for PCI Express'''. |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[0] -tag __ddr3_contr_example_if0_p0

| + | ## Do all connections you need/want |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[1] -tag __ddr3_contr_example_if0_p0

| + | ## Generate the HDL code with '''Finish''' button. |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[1] -tag __ddr3_contr_example_if0_p0

| + | # Under Quartus include the file your_project.qip and not your_project.qsys |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[1] -tag __ddr3_contr_example_if0_p0

| + | ## Find the file named *_p0_pin_map.tcl :<pre class="host">$ find . -name "*_p0_pin_map.tcl"</pre> |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[2] -tag __ddr3_contr_example_if0_p0

| + | ## It must be under directory named '''your_project/synthesis/submodules/''' |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[2] -tag __ddr3_contr_example_if0_p0

| + | ## Edit it and looking for line begining with : <code><source lang="tcl">proc YOUR_PROJECT_NAME_mem_if_ddr3_emif_0_p0_get_input_clk_id { pll_output_node_id } {</source></code> |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[2] -tag __ddr3_contr_example_if0_p0

| + | ## Add this line at the begining of function :<code><source lang="tcl">return $pll_output_node_id</source></code> |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[3] -tag __ddr3_contr_example_if0_p0

| + | ## Then synthesize all. |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[3] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[3] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[4] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[4] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[4] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[5] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[5] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[5] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[6] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[6] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[6] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[7] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[7] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[7] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[8] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[8] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[8] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[9] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[9] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[9] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[10] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[10] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[10] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[11] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[11] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[11] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[12] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[12] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[12] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[13] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[13] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[13] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[14] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[14] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[14] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[15] -tag __ddr3_contr_example_if0_p0

| + | {{Note| In one line :<pre class="host">$ find . -name "*_p0_pin_map.tcl" | xargs sed -iolt "/_mem_if_ddr3_emif_0_p0_get_input_clk_id {/a return \$pll_output_node_id"</pre>}} |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[15] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[15] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[16] -tag __ddr3_contr_example_if0_p0

| + | === Failed to find PLL reference clock === |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[16] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[16] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[17] -tag __ddr3_contr_example_if0_p0

| + | It's a known intel bug documented [https://www.altera.com/support/support-resources/knowledge-base/solutions/rd05282014_665.html here]. |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[17] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[17] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[18] -tag __ddr3_contr_example_if0_p0

| + | == IO == |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[18] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[18] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[19] -tag __ddr3_contr_example_if0_p0

| + | * [[APF6_SP_DDR3_PINOUT#Pinout_placement | Pinout placement]] |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[19] -tag __ddr3_contr_example_if0_p0

| + | * [[APF6_SP_DDR3_PINOUT#Technology_pinout | Technology pinout]] |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[19] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[20] -tag __ddr3_contr_example_if0_p0

| + | == Downloads == |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[20] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[20] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[21] -tag __ddr3_contr_example_if0_p0

| + | Soon here, some examples project to downloads. |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[21] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[21] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[22] -tag __ddr3_contr_example_if0_p0

| + | == Links == |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[22] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[22] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dq[23] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dq[23] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dq[23] -tag __ddr3_contr_example_if0_p0

| + | |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_dqs[0] -tag __ddr3_contr_example_if0_p0

| |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dqs[0] -tag __ddr3_contr_example_if0_p0

| |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dqs[0] -tag __ddr3_contr_example_if0_p0

| |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_dqs_n[0] -tag __ddr3_contr_example_if0_p0

| |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dqs_n[0] -tag __ddr3_contr_example_if0_p0

| |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dqs_n[0] -tag __ddr3_contr_example_if0_p0

| |

| | | | |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_dqs[1] -tag __ddr3_contr_example_if0_p0

| + | * [http://www.altera.com/literature/lit-external-memory-interface.jsp External Memory Interface Handbook] |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dqs[1] -tag __ddr3_contr_example_if0_p0

| + | * [http://www.altera.com/literature/hb/external-memory/emi_fd_uniphy.pdf UniPHY](pdf) |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dqs[1] -tag __ddr3_contr_example_if0_p0

| + | * [http://www.alterawiki.com/wiki/Reference_Design_-_Cyclone_V_Hard_Memory_Controller_with_Avalon_MM_data_width_expanded_for_User_ECC Reference Design - Cyclone V Hard Memory Controller with Avalon MM data width expanded for User ECC] |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_dqs_n[1] -tag __ddr3_contr_example_if0_p0

| + | * [https://www.altera.com/support/support-resources/knowledge-base/solutions/rd05282014_665.html The Clock DDR3 hack on altera website] |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dqs_n[1] -tag __ddr3_contr_example_if0_p0

| + | * [http://www.altera.com/literature/hb/external-memory/emi_uniphy_ref_EMIF_toolkit.pdf Debug toolkit ](pdf) |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dqs_n[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | | + | |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_dqs[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dqs[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dqs[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_dqs_n[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name INPUT_TERMINATION "PARALLEL 40 OHM WITH CALIBRATION" -to mem_dqs_n[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dqs_n[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | | + | |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_ck[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_ck[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 1.35-V SSTL" -to mem_ck_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_ck_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[10] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[10] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[11] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[11] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[12] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[12] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[13] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[13] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[14] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[14] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[3] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[3] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[4] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[4] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[5] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[5] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[6] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[6] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[7] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[7] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[8] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[8] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_a[9] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_a[9] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_ba[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_ba[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_ba[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_ba[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_ba[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_ba[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_cas_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_cas_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_cke[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_cke[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_cs_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_cs_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_odt[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_odt[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_ras_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_ras_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_we_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_we_n[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_reset_n -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITHOUT CALIBRATION" -to mem_reset_n -tag __ddr3_contr_example_if0_p0

| + | |

| − | | + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dm[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dm[0] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dm[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dm[1] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to mem_dm[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | set_instance_assignment -name OUTPUT_TERMINATION "SERIES 40 OHM WITH CALIBRATION" -to mem_dm[2] -tag __ddr3_contr_example_if0_p0

| + | |

| − | | + | |

| − | set_instance_assignment -name IO_STANDARD "SSTL-135" -to pll_ref_clk -tag __ddr3_contr_example_if0_p0

| + | |

| − | </pre>

| + | |

| − | | + | |

| − | == Links ==

| + | |

Diagram below describe the connections between the CycloneV and the two DDR3 blocks. Each DDR3 blocks has two banks of 128MB, on one chip (U15) all data are used, and on the other chip, only 128MB are used, the second bank is not plugged. Thus, the amount of ram accessible via the fpga is 384MB, with a data bus of 24bits.

To use the DDR3 SDRAM Controller with UniPhy provided by Quartus to instanciate the DDR3. See above how to do with Qsys.

The hard controller IP «DDR3 SDRAM Controller with UniPHY» require using and external oscillator to clock it. On APF6_SP, the all CycloneV fpga is clocked with the PCIe clock at 62.5Mhz by default.

To force Quartus to use the coreclkout as input clock for DDR3 controller a little hack must be done after HDL code is generated.

Soon here, some examples project to downloads.