Difference between revisions of "IMX6-CycloneV interface description"

(→Quartus : Avalon-MM Cyclone V Hard IP for PCI Express configuration) |

(→Links) |

||

| (43 intermediate revisions by one other user not shown) | |||

| Line 4: | Line 4: | ||

[[Category: PCIe]] | [[Category: PCIe]] | ||

| − | |||

== Introduction == | == Introduction == | ||

This article describe the bus interface configuration to communicate between i.MX6 processor and CycloneV FPGA. In i.MX6, the bus used to make communication with the FPGA is the PCI express. | This article describe the bus interface configuration to communicate between i.MX6 processor and CycloneV FPGA. In i.MX6, the bus used to make communication with the FPGA is the PCI express. | ||

| Line 25: | Line 24: | ||

* '''nperst''': set to vcc. | * '''nperst''': set to vcc. | ||

| − | * '''coreclkout''': ''' | + | * '''coreclkout''': '''62.5Mhz''' (by default) clock generated by quartus hard PCIe ip-core, used to clock design by defaut. |

| − | === Quartus : Avalon-MM Cyclone V Hard IP for PCI Express configuration === | + | === Qsys (Quartus 14.0) : Avalon-MM Cyclone V Hard IP for PCI Express configuration (CvP)=== |

| − | 3 | + | {{Note| The example project described above can be downloaded [http://www.armadeus.com/_downloads/apf6_SP/hardware/apf6_sp_cvp_example.zip here].}} |

| + | |||

| + | 3 Qsys components are required to use PCIe on apf6sp with configuration via PCIe: | ||

* Avalon-MM Cyclone V Hard IP for PCI Express : The hard ip for PCIe | * Avalon-MM Cyclone V Hard IP for PCI Express : The hard ip for PCIe | ||

| Line 40: | Line 41: | ||

* Number of lanes : '''x1''' | * Number of lanes : '''x1''' | ||

| − | + | * Reference clock frequency : '''125Mhz''' | |

| − | * Enable configuration via the PCIe link | + | * check "Enable configuration via the PCIe link" |

| − | + | * check "Use 62.5 MHz application clock" | |

* BAR0 | * BAR0 | ||

** Type: 32-bit non-prefetchable memory | ** Type: 32-bit non-prefetchable memory | ||

| − | |||

* Vendor ID: '''0x00001172''' | * Vendor ID: '''0x00001172''' | ||

* Device ID: '''0x0000e001''' | * Device ID: '''0x0000e001''' | ||

| − | * Class Code: '''0x00001300''' | + | * Class Code: '''0x00001300''': there is a bug in quartus, the actual class code is here '''13''' |

| − | + | * Maximum payload : '''128 bytes''':PCIe i.MX6's rootcomplex support only 128bytes payload maximum | |

| − | * Maximum payload : 128 bytes | + | * Size of address pages: '''4 KByte - 12 bits''': Linux use pages of 4KByte by default. |

==== Altera PCIe Reconfig Driver ==== | ==== Altera PCIe Reconfig Driver ==== | ||

| − | + | * Let all configuration by default. | |

| + | |||

| + | See «General connexion schematics» above for connexions. | ||

==== Transceiver Reconfiguration Controller ==== | ==== Transceiver Reconfiguration Controller ==== | ||

| − | + | * Let all configuration by default. | |

| − | + | See «General connexion schematics» above for connexions. | |

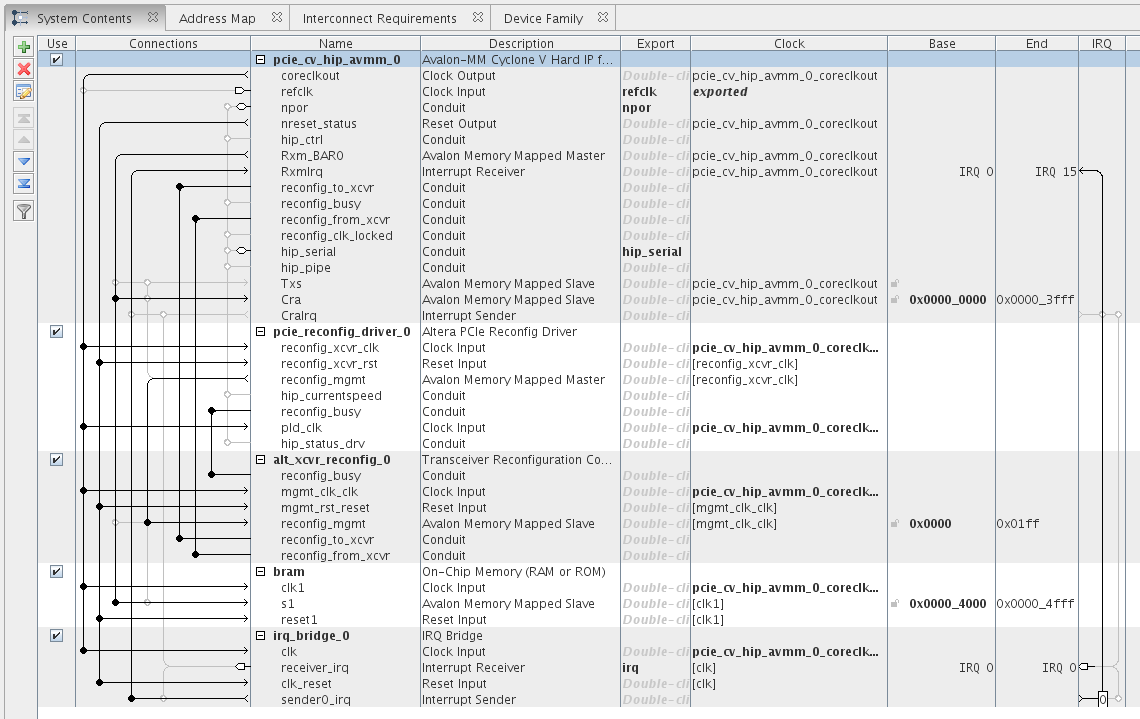

| − | + | ==== General connexion schematics ==== | |

| − | + | [[Image:fpga_cycloneV_qsys_cvp_connexion.png]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ==== Quartus configuration ==== | |

| − | + | ||

| − | # | + | To generate CvP files do : |

| − | + | ||

| + | * Add the generated qsys project under the Quartus project. | ||

| + | ** Set as top level | ||

| + | * In ''CycloneV : ...'' -> (right click) -> device ... | ||

| + | * device and pin option button | ||

| + | * Category:cvp Setting : | ||

| + | ** Configuration via protocol : '''core initialization and update''' | ||

| + | * Run synthesis | ||

| + | ** configure pinout like described in ''FPGA pinout'' above. | ||

| + | * Run place&route/assembly | ||

| + | * File -> convert programming files ... | ||

| + | ** Programming file type: '''Raw binary file (.rbf) | ||

| + | ** add file : project.sof | ||

| + | ** Check '''create CvP files''' box. | ||

| + | ** Click '''generate''' | ||

| + | * Two files are available in the project root: | ||

| + | ** '''project.periph.rbf''': For FPGA IO, to be loader with U-Boot | ||

| + | ** '''project.core.rbf''': For FPGA core, to be loader with PCIe under Linux | ||

| + | |||

| + | ==== Linux Usage ==== | ||

| + | |||

| + | See [[PCIe_fpga_load]] page to know how to load the bitstreams. | ||

| + | |||

| + | The bram of the project example can be accessed with the [[pci_debug]] tool on BAR0 at address 0x4000. | ||

| + | |||

| + | === Interrupts === | ||

| + | |||

| + | It's possible to transmit interrupts from the FPGA to the i.MX6 through the PCI express. | ||

| + | |||

| + | ==== Qsys ==== | ||

| + | |||

| + | To use it, in Qsys, simply connect your interrupt emitter on the Rxmirq conduit of the component ''Avalon-MM Cyclone V Hard IP for PCI Express'' as shown in screenshot above : | ||

| + | |||

| + | [[Image:FPGA_pcie_interrupts.png]] | ||

| + | |||

| + | Two interrupts registers are available through the '''Cra''': | ||

| + | |||

| + | {| class="wikitable" style="text-align:left; width:20%;" | ||

| + | |- | ||

| + | ! scope=col bgcolor=yellow | Addr | ||

| + | ! scope=col bgcolor=yellow | name | ||

| + | |- | ||

| + | ! scope=row bgcolor=#BBBBBB| 0x0040 | ||

| + | | bgcolor=#BBBBBB | PCI Express Interrupt Status | ||

| + | |- | ||

| + | ! scope=row bgcolor=#BBBBBB| 0x0050 | ||

| + | | bgcolor=#BBBBBB | PCI Express Interrupt Enable | ||

| + | |} | ||

| + | |||

| + | To activate interruption, simply write '1' in register ''PCI Express Interrupt Enable''. | ||

| + | |||

| + | For more information about the Avalon-mm Cyclone V interrupt see the [http://www.altera.com/literature/ug/ug_c5_pcie_avmm.pdf datasheet] (page 15). | ||

| + | |||

| + | ==== Linux ==== | ||

| + | |||

| + | An MSI interrupt example driver is available in the armadeus bsp, it can be found in directory : | ||

| + | |||

| + | target/demos/pcie_msi/ | ||

| + | |||

| + | To compile it, simply type : | ||

| + | |||

| + | <pre class="host"> | ||

| + | $ make | ||

</pre> | </pre> | ||

| + | |||

| + | Insert it in your kernel with insmod : | ||

| + | |||

| + | {{Note| Be sure that module «fpgaloader» is unloaded before loading the pcie_msi driver: <pre class="apf">$ rmmod fpgaloader</pre>}} | ||

| + | |||

| + | <pre class="apf"> | ||

| + | $ insmod pcie_msi.ko | ||

| + | </pre> | ||

| + | |||

| + | If interruption is '''enable''' in the FPGA-PCIe Ip (register 0x0050 in CRA) this message will be printed at each interrupt : | ||

| + | |||

| + | {{Note| To enable the pcie interrupt, pci_debug can be used this way :<pre class="apf">$ pci_debug -s 01:00.0 -b0 | ||

| + | PCI> c32 0x50 1 | ||

| + | PCI> q</pre> | ||

| + | }} | ||

| + | |||

| + | <pre class="apf"> | ||

| + | msi 309 | ||

| + | </pre> | ||

| + | |||

| + | (if the irq number is 309). | ||

| + | |||

| + | For more informations about the PCIe MSI Interrupts see [http://lxr.free-electrons.com/source/Documentation/PCI/MSI-HOWTO.txt the kernel documentation]. | ||

| + | |||

| + | === FPGA pinout === | ||

| + | |||

| + | FPGA pinout is the [[APF6_SP_DDR3_PINOUT#PCIe | following]] | ||

== Clocking without PCIe == | == Clocking without PCIe == | ||

PCIe_clk input can be used to clock the entire design without using the PCIe hard ip-core. But it can't be use directly, PLL must be instancied. | PCIe_clk input can be used to clock the entire design without using the PCIe hard ip-core. But it can't be use directly, PLL must be instancied. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | [[image:apf6sp_clocking_pcie.png|700px|center|thumb|'''figure 2''' - ''Clocking with PCIe Pll description'']] | |

| + | |||

| + | A blinking led example is provided in BSP under the directory '''firmware/leds/blinking_led/src/cycloneV/'''. | ||

| + | |||

| + | == Links == | ||

| + | * [[pci_debug | '''pci_debug''': a useful commands tool to access PCIe BARx]] | ||

* [http://www.altera.com/literature/ug/ug_c5_pcie_avmm.pdf Avalon-MM to PCIe interface for CycloneV] | * [http://www.altera.com/literature/ug/ug_c5_pcie_avmm.pdf Avalon-MM to PCIe interface for CycloneV] | ||

| + | * [https://community.nxp.com/docs/DOC-95014 NXP PCIe i.MX6 benchmarks] | ||

Latest revision as of 14:44, 7 August 2017

Contents

Introduction

This article describe the bus interface configuration to communicate between i.MX6 processor and CycloneV FPGA. In i.MX6, the bus used to make communication with the FPGA is the PCI express.

PCIe

PCIe used to do the communication between i.MX6 and CycloneV is a Gen1 with one lane. By defaut, Armadeus recommend to use the quartus ip-core Cyclone V Avalon-MM Interface for PCIe.

Simplified view

Figure 1 is a simplified view of APF6 schematics, signals are :

- PCIE_CLK: 125Mhz differential pcie clock (PCIE_CLKN and PCIE_CLKP).

- PCIE_RX: Differential receive pcie signal lane0 (PCIE_RXN and PCIE_RXP).

- PCIE_TX: Differential transmit pcie signal lane0(PCIE_TXN and PCIE_TXP).

- npor: set to Vcc.

- nperst: set to vcc.

- coreclkout: 62.5Mhz (by default) clock generated by quartus hard PCIe ip-core, used to clock design by defaut.

Qsys (Quartus 14.0) : Avalon-MM Cyclone V Hard IP for PCI Express configuration (CvP)

| |

Note: The example project described above can be downloaded here. |

3 Qsys components are required to use PCIe on apf6sp with configuration via PCIe:

- Avalon-MM Cyclone V Hard IP for PCI Express : The hard ip for PCIe

- Altera PCIe Reconfig Driver

- Transceiver Reconfiguration Controller

Avalon-MM Cyclone V Hard IP for PCI Express

To use the Altera IP on the APF6_SP configure it as following :

- Number of lanes : x1

- Reference clock frequency : 125Mhz

- check "Enable configuration via the PCIe link"

- check "Use 62.5 MHz application clock"

- BAR0

- Type: 32-bit non-prefetchable memory

- Vendor ID: 0x00001172

- Device ID: 0x0000e001

- Class Code: 0x00001300: there is a bug in quartus, the actual class code is here 13

- Maximum payload : 128 bytes:PCIe i.MX6's rootcomplex support only 128bytes payload maximum

- Size of address pages: 4 KByte - 12 bits: Linux use pages of 4KByte by default.

Altera PCIe Reconfig Driver

- Let all configuration by default.

See «General connexion schematics» above for connexions.

Transceiver Reconfiguration Controller

- Let all configuration by default.

See «General connexion schematics» above for connexions.

General connexion schematics

Quartus configuration

To generate CvP files do :

- Add the generated qsys project under the Quartus project.

- Set as top level

- In CycloneV : ... -> (right click) -> device ...

- device and pin option button

- Category:cvp Setting :

- Configuration via protocol : core initialization and update

- Run synthesis

- configure pinout like described in FPGA pinout above.

- Run place&route/assembly

- File -> convert programming files ...

- Programming file type: Raw binary file (.rbf)

- add file : project.sof

- Check create CvP files box.

- Click generate

- Two files are available in the project root:

- project.periph.rbf: For FPGA IO, to be loader with U-Boot

- project.core.rbf: For FPGA core, to be loader with PCIe under Linux

Linux Usage

See PCIe_fpga_load page to know how to load the bitstreams.

The bram of the project example can be accessed with the pci_debug tool on BAR0 at address 0x4000.

Interrupts

It's possible to transmit interrupts from the FPGA to the i.MX6 through the PCI express.

Qsys

To use it, in Qsys, simply connect your interrupt emitter on the Rxmirq conduit of the component Avalon-MM Cyclone V Hard IP for PCI Express as shown in screenshot above :

Two interrupts registers are available through the Cra:

| Addr | name |

|---|---|

| 0x0040 | PCI Express Interrupt Status |

| 0x0050 | PCI Express Interrupt Enable |

To activate interruption, simply write '1' in register PCI Express Interrupt Enable.

For more information about the Avalon-mm Cyclone V interrupt see the datasheet (page 15).

Linux

An MSI interrupt example driver is available in the armadeus bsp, it can be found in directory :

target/demos/pcie_msi/

To compile it, simply type :

$ make

Insert it in your kernel with insmod :

| |

Note: Be sure that module «fpgaloader» is unloaded before loading the pcie_msi driver: $ rmmod fpgaloader |

$ insmod pcie_msi.ko

If interruption is enable in the FPGA-PCIe Ip (register 0x0050 in CRA) this message will be printed at each interrupt :

| |

Note: To enable the pcie interrupt, pci_debug can be used this way :$ pci_debug -s 01:00.0 -b0 PCI> c32 0x50 1 PCI> q |

msi 309

(if the irq number is 309).

For more informations about the PCIe MSI Interrupts see the kernel documentation.

FPGA pinout

FPGA pinout is the following

Clocking without PCIe

PCIe_clk input can be used to clock the entire design without using the PCIe hard ip-core. But it can't be use directly, PLL must be instancied.

A blinking led example is provided in BSP under the directory firmware/leds/blinking_led/src/cycloneV/.