Difference between revisions of "OPOS6UL SP"

From ArmadeusWiki

(Created page with "Category: OPOS6UL_SP Category:MainBoards Category:Hardware {{under construction}} == Description == File:OPOS6UL_SP.png The OPOS6UL_SP is a [https://en.wik...") |

|||

| (12 intermediate revisions by the same user not shown) | |||

| Line 3: | Line 3: | ||

[[Category:Hardware]] | [[Category:Hardware]] | ||

| − | |||

| − | |||

== Description == | == Description == | ||

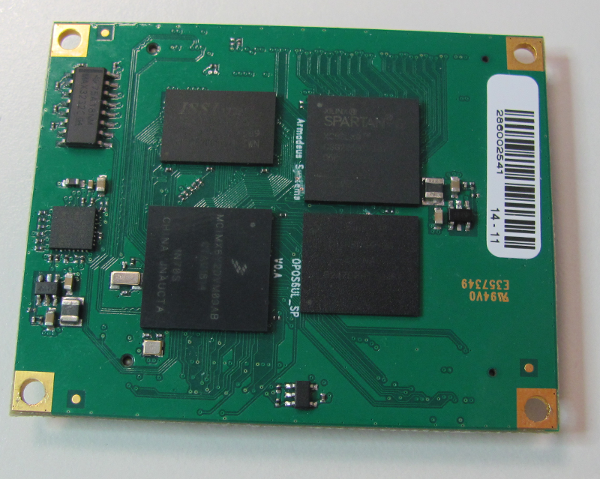

[[File:OPOS6UL_SP.png]] | [[File:OPOS6UL_SP.png]] | ||

| − | The OPOS6UL_SP is a [https://en.wikipedia.org/wiki/Single-board_computer Single Board Computer] with a FPGA. | + | |

| + | The OPOS6UL_SP is a [https://en.wikipedia.org/wiki/Single-board_computer Single Board Computer] with a FPGA. This board is mainly pin-to-pin compatible with the APF27. The objective is to replace APF27 with minimum electronic and software refactoring. | ||

Here is a list of the main features: | Here is a list of the main features: | ||

* Processor: [https://www.nxp.com/products/processors-and-microcontrollers/applications-processors/i.mx-applications-processors/i.mx-6-processors/i.mx-6ull-single-core-processor-with-arm-cortex-a7-core:i.MX6ULL i.MX6ULL] (i.MX6ULL single A7 @ 800 or 900MHz) | * Processor: [https://www.nxp.com/products/processors-and-microcontrollers/applications-processors/i.mx-applications-processors/i.mx-6-processors/i.mx-6ull-single-core-processor-with-arm-cortex-a7-core:i.MX6ULL i.MX6ULL] (i.MX6ULL single A7 @ 800 or 900MHz) | ||

| + | * FPGA: [https://www.xilinx.com/products/silicon-devices/fpga/spartan-6.html Spartan6 LX9] | ||

TODO | TODO | ||

| Line 22: | Line 22: | ||

==Features list== | ==Features list== | ||

| − | * [[ | + | * [[OPOS6UL_SP Linux kernel status]] |

{| border="0" cellpadding="5" cellspacing="5" summary="Hardware Add-Ons by functionnalities" | {| border="0" cellpadding="5" cellspacing="5" summary="Hardware Add-Ons by functionnalities" | ||

| Line 28: | Line 28: | ||

|- style="background:#f4f4f4; color:black; -moz-border-radius:18px;" | |- style="background:#f4f4f4; color:black; -moz-border-radius:18px;" | ||

| | | | ||

| + | === FPGA === | ||

| + | |||

| + | * [[OPOS6UL_SP_Interfaces_description | Spartan6]] | ||

| + | |||

===Video=== | ===Video=== | ||

====Video Out==== | ====Video Out==== | ||

| Line 48: | Line 52: | ||

|| | || | ||

| − | |||

| − | |||

| − | |||

| − | |||

===Storage=== | ===Storage=== | ||

| Line 64: | Line 64: | ||

==Development boards== | ==Development boards== | ||

| − | * [[ | + | * [[OPOS6UL_SPDev]] |

| + | * [[APF27Dev]] | ||

Latest revision as of 10:55, 22 July 2020

Contents

Description

The OPOS6UL_SP is a Single Board Computer with a FPGA. This board is mainly pin-to-pin compatible with the APF27. The objective is to replace APF27 with minimum electronic and software refactoring.

Here is a list of the main features:

- Processor: i.MX6ULL (i.MX6ULL single A7 @ 800 or 900MHz)

- FPGA: Spartan6 LX9

TODO

Resources

TODO

Features list

FPGAVideoVideo OutVideo In |

Wired communication |

StorageOther |