Difference between revisions of "Opos6ul sp fpga simple howto"

From ArmadeusWiki

(Created page with "Category: opos6ul_sp = Introduction =") |

|||

| (7 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | [[Category: | + | [[Category: OPOS6UL_SP]] |

| − | + | [[Category: FPGA]] | |

| + | [[Category: Verilog]] | ||

| + | {{Under_Construction}} | ||

= Introduction = | = Introduction = | ||

| + | |||

| + | This page is a step-by-step tutorial to explain how to develop with FPGA (spartan6) on [[OPOS6UL_SP]] Armadeus board. | ||

| + | |||

| + | = Architecture = | ||

| + | |||

| + | [[File:opos6ul_sp_fpga_tuto_01.png|center]] | ||

| + | |||

| + | In this tutorial, a simple FPGA design will be done. The objective is to instanciate a block of RAM in the FPGA and be able to read and write data in it from U-Boot then Linux. | ||

| + | |||

| + | = Software tools = | ||

| + | |||

| + | A recent Armadeus BSP is required. | ||

| + | <pre class="host"> | ||

| + | $ git clone git://git.code.sf.net/p/armadeus/code op6sp | ||

| + | $ cd op6sp | ||

| + | $ make | ||

| + | $ make opos6ulsp_defconfig | ||

| + | $ make | ||

| + | </pre> | ||

| + | |||

| + | = Hardware description = | ||

| + | |||

| + | = Links = | ||

| + | |||

| + | * [[OPOS6UL_SP]] | ||

| + | * [[OPOS6UL_SP_Interfaces_description]] | ||

Latest revision as of 11:32, 22 July 2020

Page under construction...

Informations on this page are not guaranteed !!

Informations on this page are not guaranteed !!

Introduction

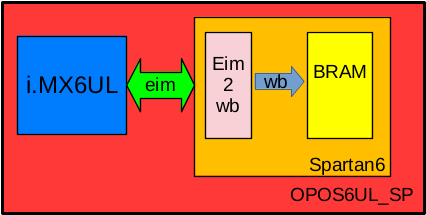

This page is a step-by-step tutorial to explain how to develop with FPGA (spartan6) on OPOS6UL_SP Armadeus board.

Architecture

In this tutorial, a simple FPGA design will be done. The objective is to instanciate a block of RAM in the FPGA and be able to read and write data in it from U-Boot then Linux.

Software tools

A recent Armadeus BSP is required.

$ git clone git://git.code.sf.net/p/armadeus/code op6sp $ cd op6sp $ make $ make opos6ulsp_defconfig $ make